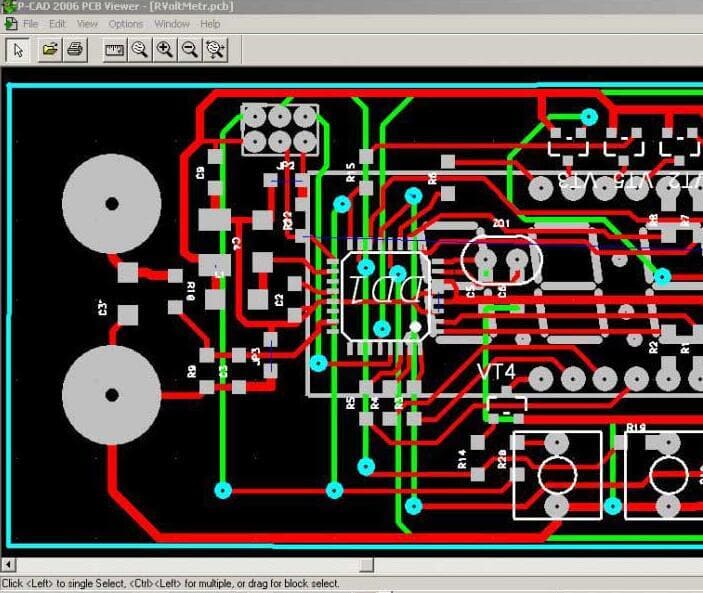

PCB design process is divided into six steps: network table input, rule setting, component layout, wiring, inspection, review and output. Last article we introduce the first 5 steps. Here we will introduce the last step: design output.

Design Output

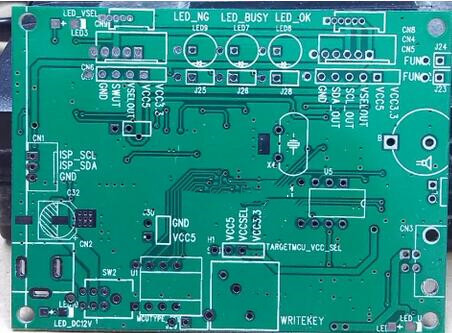

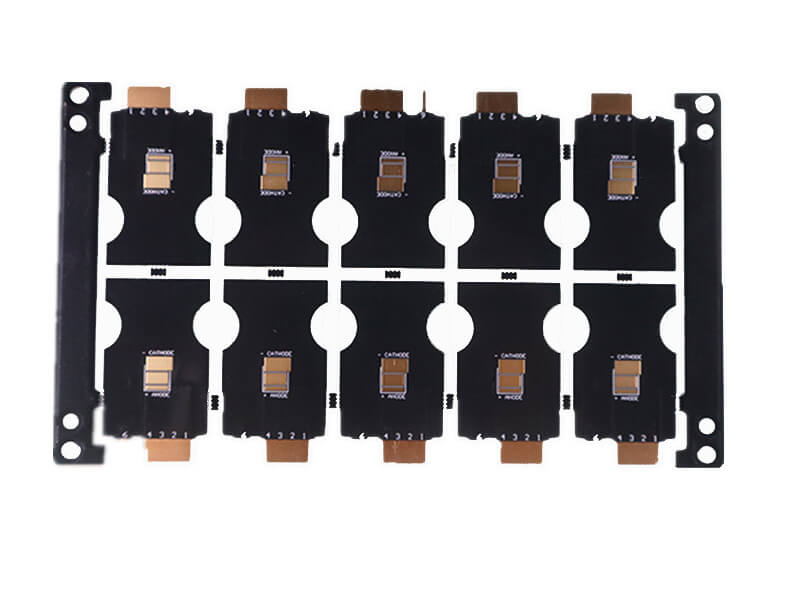

PCB design can be output to printer or output photo drawing file. The printer can print PCB layers, which is convenient for designers and reviewers to check; Photo drawing documents shall be handed over to the board manufacturer to produce printed boards. The output of photo drawing file is very important, which is related to the success or failure of this design. The following will focus on the notes for output photo drawing documents.

- The layers to be output include wiring layer (including top layer, bottom layer, middle wiring layer), power layer (including VCC layer and GND layer), silk screen layer (including top screen printing, bottom screen printing), welding resistance layer (including top layer resistance welding and bottom layer resistance welding), and also generate drilling file (NC drill).

- If the power layer is set to split/mixed, select routing in the document item of the add document window, and copper coating shall be carried out on PCB drawing using plan connect of pour manager before outputting photo drawing file; If set to cam plan, select plan. When setting layer item, add layer 25, and select pads and viasc in layer 25. In the device setup window (press device setup), change the value of aperture to 199.

- When setting the layer for each layer, select board outline.

- When setting the layer of the screen printing layer, do not select part type, and select the outline, text and line of the top (bottom) and screen printing layer.

- When setting layer of welding resistance layer, selecting through hole means that there is no resistance welding on the hole, and if no hole is selected, it means home resistance welding, and it is determined according to the specific situation.

- When generating drilling files, use the default settings of PowerPCBwithout any changes.

- After all photo drawing documents are output, they are opened and printed with CAM350. The designers and reviewers check the vias according to the “PCB Checklist” as one of the important components of multi-layer PCB. The cost of drilling usually accounts for 30-40% of PCB board making cost. In short, each hole in a PCB can be called a through hole.

From the perspective of function, the through hole can be divided into two categories: one is to be used as the electrical connection between the layers; The second is to fix or locate the device.

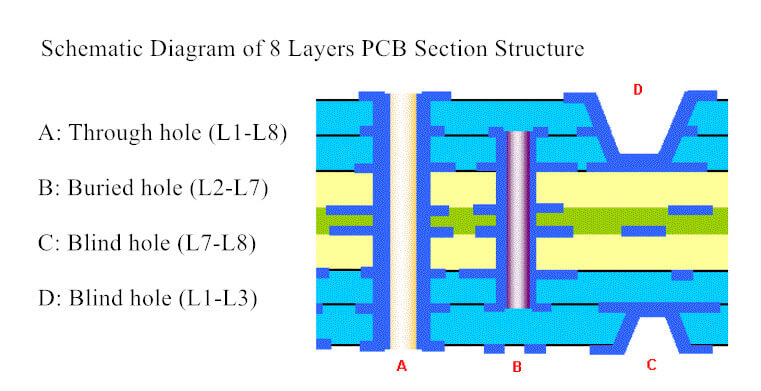

If the process is concerned, these vias are generally divided into three categories, namely blind via, buried via and through via. Blind holes are located on the top and bottom surfaces of printed circuit boards, with a certain depth, which is used for the connection of surface lines and inner lines below. The depth of holes usually does not exceed a certain ratio (aperture). The embedded hole refers to the connection hole located in the inner layer of printed circuit board, which will not extend to the surface of the circuit board. The two types of holes are located in the inner layer of the circuit board. Before laminating, through hole forming process is used to complete the process. Several inner layers may be overlapped during the formation of the through hole. The third is called through hole, which passes through the whole circuit board and can be used for internal interconnection or installation and positioning hole as a component. Because through hole is easier to realize and cost is lower, most PCB uses it, instead of two other kinds of vias. The hole passing mentioned below, if there is no special description, shall be considered as through hole.

From the design point of view, a through hole is mainly composed of two parts, one is the drill hole in the middle, and the other is the pad area around the drill hole. The size of these two parts determines the size of the via. Obviously, in the design of high-speed and high-density PCB, designers always hope that the smaller the vias, the better, so that more wiring space can be left on the board. In addition, the smaller the vias, the smaller the parasitic capacitance, which is more suitable for high-speed circuits. However, the decrease of the hole size also brings about the increase of the cost, and the size of the through hole can not be reduced unlimited. It is limited by the drilling and plating technology: the smaller the hole is, the longer the drilling time is, and the easier it is to deviate from the center position; And when the depth of the hole is more than 6 times of the diameter of the hole, it can not guarantee the uniform copper plating of the hole wall. For example, the thickness (through-hole depth) of a normal 6-layer PCB is about 50 Mil, so the minimum hole diameter that PCB manufacturers can provide can only reach 8 mil.

Parasitic capacitance of through hole

The parasitic capacitance to the ground exists in the through hole itself. If the diameter of the isolation hole on the floor layer is known to be D2, the diameter of the through hole pad is D1, the thickness of PCB is T, and the dielectric constant of the substrate is ε, The parasitic capacitance of the over hole is similar to that of the following:

C=1.41 ε TD1/(D2-D1)

The main effect of parasitic capacitance through the hole is to extend the rising time of the signal and reduce the speed of the circuit. For example, for a PCB with a thickness of 50mil, if the diameter of the pad is 10mil and the diameter of the pad is 20MIL, and the distance between the pad and the copper laying area is 32mil, we can approximately calculate the parasitic capacitance of the hole by the formula above: c= 1.41×4.4×0.050×0.020/ (0.032-0.020) =0.517pf, The rise time variation caused by this part of capacitance is: t10-90=2.2c (z0/2) =2.2×0.517x (55/2) =31.28ps. From these values, although the effect of the rise and delay caused by parasitic capacitance of a single through hole is not obvious, the designer should consider it carefully if the over hole is used for layer switching several times in the routing.

Parasitic inductance of through hole

In the design of high-speed digital circuit, the parasitic inductance of the over hole often brings more harm than parasitic capacitance. Its parasitic series inductor will weaken the contribution of bypass capacitance and the filtering effect of the whole power system. We can simply calculate a parasitic inductance with the approximate over hole by using the following formula:

L = 5.08h [ln (4h/d) +1] where l refers to the inductance of the through hole, h is the length of the hole, and D is the diameter of the center hole. From the formula, it can be seen that the diameter of the through hole has little influence on the inductance, and the most important influence on the inductance is the length of the through hole. The inductance of the over hole can be calculated as follows: l = 5.08×0.050 [ln (4×0.050/0.010) +1] =1.015nh. If the rise time of the signal is 1ns, the equivalent impedance is XL= π L/T10-90=3.19 Ω。 Such impedance can not be ignored when high frequency current is passed. Especially, when connecting power layer and stratum, bypass capacitance needs to pass through two vias, so that parasitic inductance of the through hole will multiply.

Via Design in High Speed PCB

Through the above analysis of parasitic characteristics of vias, we can see that in high-speed PCB design, seemingly simple vias often bring great negative effects to circuit design. In order to reduce the adverse effects caused by the parasitic effect of vias, the following measures can be taken in the design:

- Considering the cost and signal quality, the reasonable size of via is selected. For example, for 6-10 layer memory module PCB design, it is better to select 10 / 20 mil (drilling / pad) via. For some high-density small size boards, you can also try to use 8 / 18 mil via. Under the current technical conditions, it is difficult to use smaller size vias. For power or ground via, larger size can be considered to reduce impedance.

- From the two formulas discussed above, it can be concluded that using thinner PCB is beneficial to reduce the two parasitic parameters of vias.

- The signal wiring on PCB board should not be changed as much as possible. In other words, unnecessary vias should not be used.

- The pins of power supply and ground should be perforated nearby. The shorter the lead between the via and pins, the better, because they will lead to the increase of inductance. At the same time, the power and ground leads should be as thick as possible to reduce the impedance.

In order to provide the nearest loop for the signal, some grounded vias are placed near the vias of the signal layer. Even a large number of redundant ground vias can be placed on the PCB board. Of course, we need to be flexible in design. The via model discussed above is the case that each layer has pads. Sometimes, we can reduce or even remove the pads of some layers. Especially when the density of vias is very high, it may lead to the formation of a cut-off slot in the copper layer. To solve this problem, besides moving the position of vias, we can also consider reducing the pad size of vias in the copper layer.